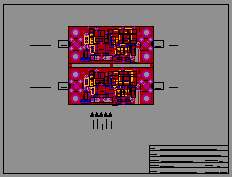

Per scaricare tutti gli schemi ed i disegni dei PCB in formato Circad98 cliccare qui.

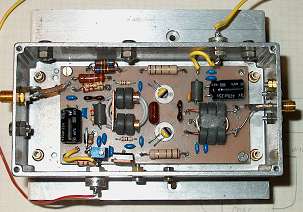

Ricetrasmettitore "HF 2001":

DETTAGLIO DEI CIRCUITI

N.B.: Per una visione migliore degli schemi é consigliabile installare la versionde demo di Circad

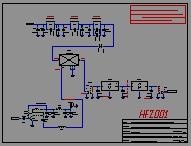

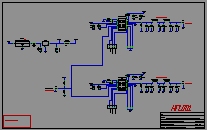

Il circuito d'ingresso è costituito dai seguenti blocchi:

a) Filtro passa basso 30 MHz;

b) Mixer di medio livello;

c) Filtro passa banda a 45 MHz;

d) Amplificatore del segnale eterodina.

Descrizione dei circuiti.

a) Il passa basso d'ingresso (o di uscita nella funzione trasmettitore) è costituito da un filtro ellittico a 5 celle con attenuazione fuori banda di almeno 50 dB e perdita di inserzione inferiore a 0,2 dB.

Per una corretta taratura è necessario, una volta realizzato, regolare le induttanze L1, L2 ed L3 per ottenere gli "infiniti" alla corretta frequenza di risonanza con le rispettive capacità.

b) La conversione è affidata ad un Mixer che lavora con un livello di eterodina di + 17 dBm (medio livello) che permette di avere un intercept- point superiore ai + 20 dBm, valore già sufficiente per lavorare nella gamma HF anche in condizioni gravose, se si utilizza una buona antenna risuonante sulla frequenza di lavoro, anche senza l'utilizzo dei filtri di sub-ottava comunque previsti nella fase di ampliamento successiva.

c) Il filtro passa banda alla frequenza di 45 MHz, valore della prima FI, è realizzato con 2 filtri monolitici aventi una banda passante complessiva di 7 Khz; la perdita complessiva, una volta ben adattati, non supera i 3 dB (valore tipico 2,7 dB).

d) L'amplificatore del segnale eterodina è realizzato con un semplice BFR91 il cui guadagno, nella banda di frequenze utilizzata, è attorno ai 18 dB e consente quindi di ottenere i + 17 dBm necessari con un segnale d'ingresso di poco inferiore a 0 dBm.

Questo amplificatore è realizzato utilizzando un solo BF981, Mosfet dual-gate a basso rumore, che permette di ottenere 26 dB di guadagno alla frequenza di 45 MHz con una figura di rumore che non supera 1 dB.

L'utilizzo di un Mosfet garantisce una buona immunità ad eventuali sovraccarichi dovuti ai segnali che dovessero passare nella banda passante del filtro a 45 MHz; un valore di figura di rumore così bassa permette inoltre di avere una figura di rumore complessiva del ricevitore inferiore ad 11 dB, garantendo una eccellente sensibilità anche nella porzione più alta della gamma HF.

In trasmissione è necessario, per contenere l'eccessivo guadagno dello stadio, che l'amplificatore venga preceduto da un attenuatore il cui valore è normalmente di 12 dB.

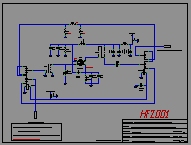

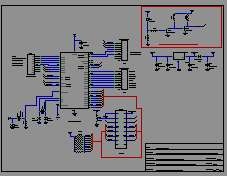

Questo blocco raccoglie 2 stadi: l'oscillatore alla frequenza di 47,052 MHz per l'USB ed alla frequenza di 48,048 MHz per l'LSB; il miscelatore realizzato con un semplice Mixer a + 7 dBm.

L'oscillatore è realizzato con un BFR91 e la commutazione delle frequenze avviene per mezzo di 2 diodi PIN; questo è stato possibile in quanto le due frequenze distano soltanto 96 KHz, cioè poco più del 2‰ rispetto alla frequenza utilizzata.

Uno stadio amplificatore separatore, realizzato sempre con un BFR91, permette di portare il livello dell'oscillatore ai + 7 dBm necessari al Mixer passivo utilizzato.

Questo blocco è composto dai 2 filtri meccanici per le bande SSB e CW che, grazie agli opportuni trasformatori, sono adattati a 50 Ω ed hanno una perdita di inserzione ≤ a 0,2 dB.

Inoltre il filtro SSB, ha sì una larghezza di banda telefonica 300 ÷ 3.400 Hz, ma ha un fattore di forma dell'ordine di 1,2 ed anche una ondulazione in banda che non supera gli 0,2 dB.

In ricezione il segnale, dopo essere passato dal filtro di banda, viene applicato direttamente all'amplificatore a 48 KHz mentre, in trasmissione, i filtri sono preceduti da un amplificatore che in banda laterale lavora sulla DSB generata dal modulatore.

Questo amplificatore, dovendo lavorare su un'impedenza di 50 Ω, è stato realizzato in due stadi: il primo che lavora in classe A mentre il secondo lavora in classe AB1 con un circuito single-ended per contenerne al massimo il consumo.

In questo amplificatore è concentrato quasi tutto il guadagno necessario al corretto funzionamento del ricevitore; il segnale proveniente dal filtro a di banda livello di – 100 dBm viene amplificato fino a portarlo al livello di 0 dBm.

L'amplificazione è suddivisa in 4 parti, la prima è dovuta all'innalzamento della tensione frutto del trasformatore risuonante T1 che, oltre a fare la funzione di filtro, eleva la tensione presente all'ingresso su impedenza di 50 Ω ad un valore 30 volte, pari a quasi 30 dB, per effetto dell'aumento di impedenza all'ingresso del Mosfet (47 KΩ).

Gli altri 70 dB sono ripartiti fra il guadagno del Mosfet (circa 20 dB) ed i due amplificatori aperiodici formati da Q3 e Q4 (circa 25 dB cadauno).

Il controllo automatico di guadagno agisce sia sui due attenuatori variabili formati dai diodi PIN che, in secondo luogo, sul G2 del Mosfet, per avere un controllo complessivo di 85 dB.

Questo blocco è costituito da un Mixer che lavora a 48 KHz che funziona in modo reversibile per la ricezione e la trasmissione, un filtro passa basso 2,2 KHz (opzionale) e l'amplificatore audio per la ricezione e l'amplificatore microfonico per la trasmissione.

Inoltre è inserito, sempre in questo blocco, l'amplificatore del segnale eterodina (BFO) o di generazione in trasmissione, che porta il livello da – 20 dBm ai + 7 dBm necessari al Mixer; anche questo amplificatore è costituito da uno stadio che lavora in classe A ed un single-ended che lavora in casse AB1 per contenerne il consumo.

La commutazione ricezione/trasmissione avviene con diodi PIN ed inoltre, attraverso il transistor Q6, si portano in conduzione i diodi del Mixer facendo transitare il segnale a 48 KHz per la trasmissione in CW.

Il passa-basso 2,2, KHz è un filtro ellittico a 5 poli ed è inseribile per contenere la banda ricevuta che altrimenti si estende fino a 3.400 Hz.

L'amplificazione audio è ottenuta mediante un normale circuito integrato anche questo a basso consumo, mentre l'amplificatore microfonico per la trasmissione è costituito da 3 stadi realizzati: il primo con una sezione di un TL082, guadagno 40 dB; il secondo con l'altra sezione del TL082, guadagna 33 dB e quindi funziona da "clipper" nei picchi del segnale microfonico; il terzo è realizzato anche questo con n circuito single-ended per lavorare in classe AB1 ed avere la necessaria bassa impedenza per pilotare il modulatore bilanciato.

Questo è il circuito che genera il segnale eterodina variabile di prima conversione; è costituito da un oscillatore di tipo Colpitts ed è suddiviso in due bande (45 ÷ 60 MHz e 60 ÷ 75 MHz) per ridurne la criticità e migliorare il rumore di fase dell'intera eterodina.

L'oscillatore è seguito da un separatore che provvede ad inviare il segnale sia al circuito amplificatore di eterodina inserito nel blocco Front-end con il giusto livello, sia all'integrato divisore per 40 presente nel blocco comparatore di fase.

Il blocco comprende il circuito integrato che divide per 40 il segnale eterodina proveniente dal VCO, due circuiti amplificatori squadratori inseriti per migliorare il funzionamento del comparatore e quindi il rumore di fase; il circuito integrato comparatore di fase ed il filtro di loop costituito dalle resistenze R5 ed R6 e dai condensatori C30 ÷ C32.

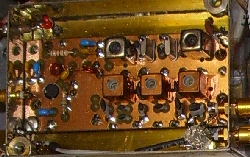

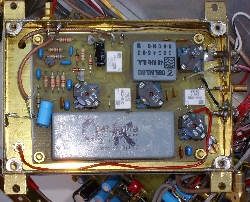

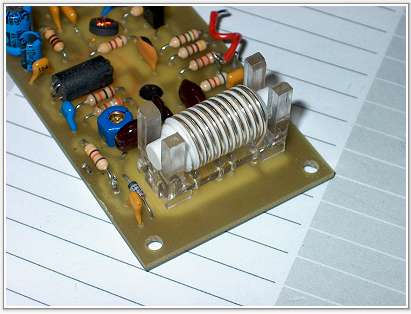

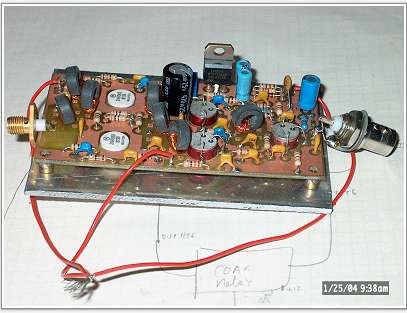

L'amplificatore pilota è costituito da 3 stadi, ha un guadagno complessivo nell'intera banda HF 1,5 ÷ 30 MHz di 33 dB e viene utilizzato con una potenza di uscita massima di 1 Watt (+ 30 dBm).

Il guadagno complessivo è stato tenuto volutamente basso, gli stadi sono molto controreazionati per ottenere complessivamente una risposta in frequenza molto piatta (ondulazione massima 0,6 dB) ed un basso livello di intermodulazione (≤ 36 dB sul livello PeP); per questo scopo sono stati anche utilizzati transistori con frequenza di lavoro V o UHF.

Il primo stadio lavora in classe A mentre i due successivi sono in configurazione controfase e lavorano in classe AB1.

Tutti i trasformatori e le induttanze sono

realizzate su

toroidi Siemens ø

L'amplificatore finale impiega 2 transistori per VHF da 25 Watt a 175 MHz, quindi è ben marginato per il suo utilizzo, tanto da risentire poco di eventuali anche forti disadattamenti ed inoltre, con il grado di controreazione utilizzato e la piccola compensazione sull'attenuatore di ingresso, mantiene pressoché inalterato il suo guadagno in tutta la banda HF che è di 13 dB.

Le due resistenze NTC vanno collocate a contatto della testa dei due transistori con del grasso al silicone, transistori che vanno dissipati adeguatamente su un dissipatore che abbia non più di 3°C/W.

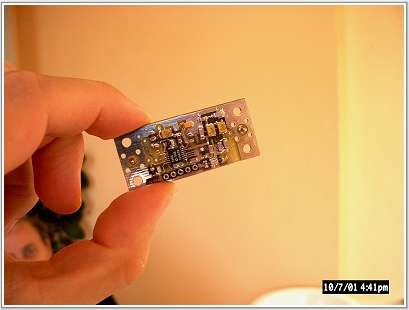

---> realizzazioni